安路科技PH1A系列FPGA定位高性价比逻辑器件,针对高带宽应用场景,能够在保持低功耗的前提下,提供同类最佳的收发器和信号处理功能。

PH1A系列FPGA集成的第三代PCIe硬核控制器,带宽最高可达8Gbit/s、可通过TD软件的IP GEN配置。该核架构广泛应用于通信设备、网络接口卡、存储系统等领域,具有高性能、低成本等特点。

SGDMA支持属性:

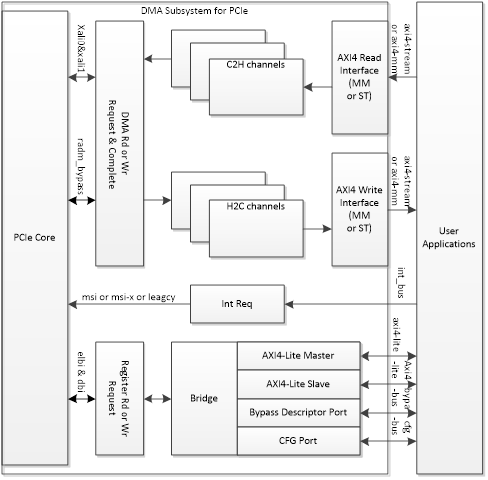

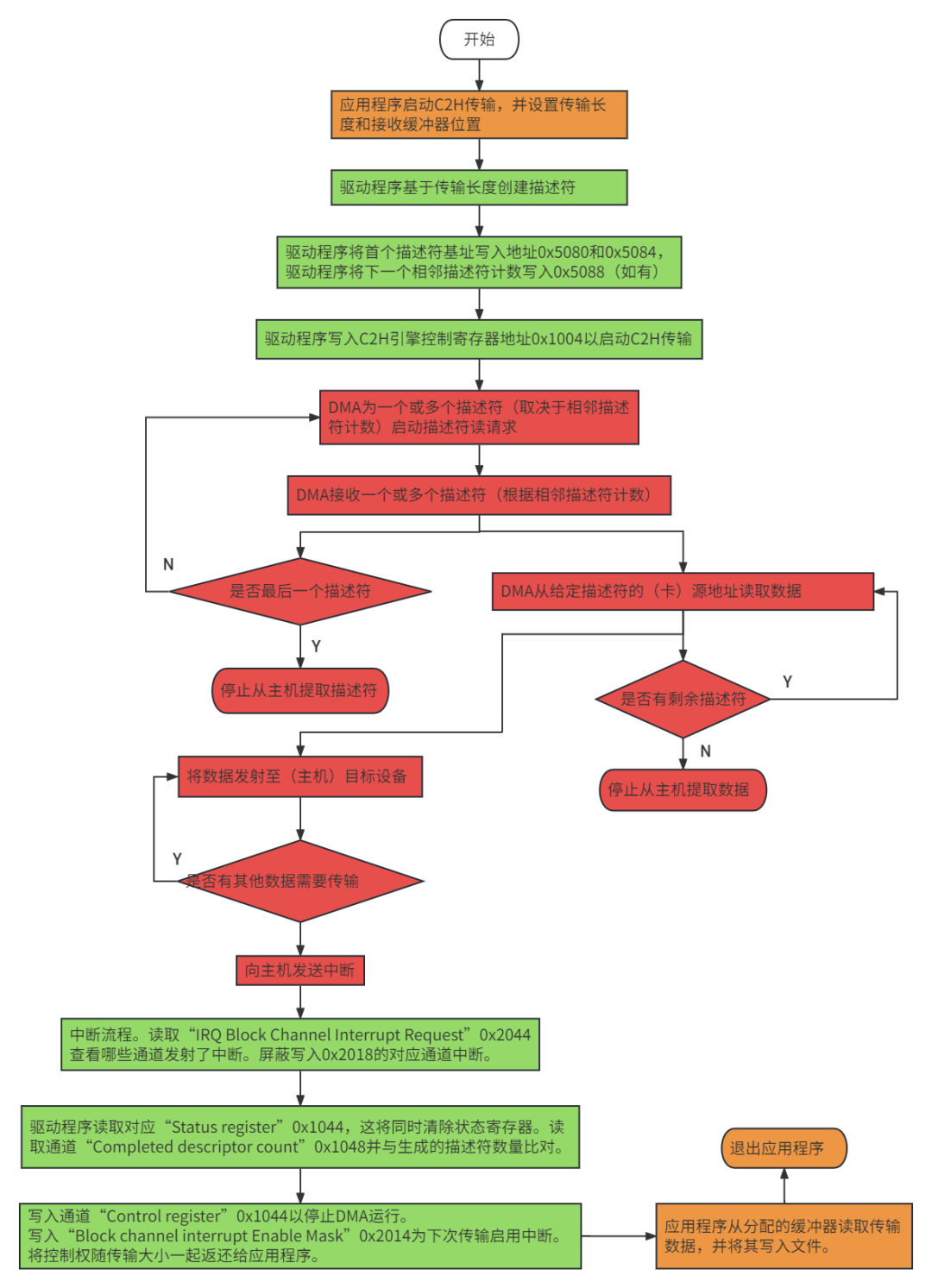

64bit和128bit(PH1A90、PH1A180)数据位宽 32bit或64bit源地址、目的地址和描述符地址 目前支持单通道C2H以及单通道H2C 后续版本将支持N通道C2H以及N通道H2C 可选的单通道AXI4-Stream接口或AXI4-MM(memory mapped)接口 支持AXI4-Lite Master读写用户和DMA寄存器 支持AXI4-Lite Slave读DMA状态寄存器 支持Scatter Gather描述符列表和环形描述符列表,列表大小无限制 MSI-X中断 (后续支持) Bypass descriptor 通道 (后续支持) 图1:DMA框图 SGDMA工作流程: SGDMA工作分为两个流程,H2C(Host to Card)和C2H(Card to Host)。 DMA C2H 方向传输摘要: 图2:C2H传输框图 首先,应用程序启动C2H传输,并设置传输长度和用于存储数据的缓冲器位置。然后,驱动程序会基于传输长度创建描述符,并将信息写入寄存器控制传输启动。DMA开始启动描述符提取请求,之后DMA接收到描述符,判断是否为最后一个描述符,如果是则停止,否则继续发送描述符提取请求。DMA会根据接收的描述符向(板卡)源地址发送读请求,读请求会持续到没有剩余描述符,并从板卡的AXI4(MM或者Stream)接口上接收数据,向主机发送数据,数据发送完毕以后向主机发送中断。 驱动程序将执行中断流程,并读取完成描述符计数寄存器,与生成的描述符数量对比。随后将控制权随传输大小一起返还给应用程序。应用程序从分配的缓冲器读取传输数据,并将其写入文件。文件写入完成后,退出应用程序。 H2C的流程与C2H的类似,主要的不同点为C2H将板卡的数据发送给主机,H2C接收主机的数据。 图3:H2C传输框图

上海安路科技于2020年12月底正式成为PCI-SIG协会新会员。加入PCI-SIG协会后,安路科技将获得更为广泛的服务、了解最新的PCI技术动态,同时能参与PCI技术法规研讨会、参与规范修订和补充建议、PCI技术支持、获得Vendor ID分配等系列服务与支持,这些都将助力公司研发技术和技术创新的稳步提升与发展。 技术预告: 2023年5月31日,安路科技即将推出SGDMA AXI4-ST(PH1A) 8CH,让我们敬请期待! 技术支持: 安路科技提供丰富的设计工具帮助用户有效地利用PH1A平台实现复杂设计。业界领先的综合和布局布线工具,同时提供各种 IP资源,方便用户直接调用调试,解决了复杂逻辑带来的资源不足的问题,为用户设计高质量产品提供有力保障。

elexcon深圳国际电子展由创意时代与博闻创意创立于2004年,已成为备受海内外电子行业关注的年度专业电子展之一,是展示技术实力、拓展行业合作的重要平台。更多展会详情请登录www.bljsleep.com 展位、赞助商及演讲人申请请联系:0755-88311535

扫描以下二维码分享至微信朋友圈:

打开微信“扫一扫”即可将该新闻分享到朋友圈。